RISC-V

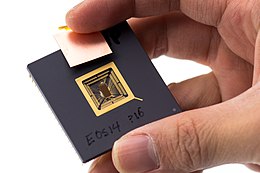

RISC-V Prototípus processzor a RISC-V architektúrával 2013 januárjában

Prototípus processzor a RISC-V architektúrával 2013 januárjában

| típus | RISC ISA , projekt , utasításkészlet , informatikai platform |

|---|---|

| Weboldal | riscv.org |

A RISC-V (kiejtve angolul: "RISC five", azaz "öt RISC") egy utasításkészlet-architektúra (ISA utasításkészlet-architektúra). A RISC nyitott és ingyenes , beleértve a 32, 64 és 128 bites c, azaz nyitott specifikációkat, amelyek az oktatás, a kutatás és az ipar szabadon felhasználhatja. Különböző SoC-kben valósítják meg , fedélzeti, összekapcsolt objektumok számára (különböző valós idejű rendszerek vagy fedélzeten támogatottak) , például Arduino , FreeRTOS , HarmonyOS , LiteOS , RT-Thread , RustOS , Zephyr .. .), könnyű számítógépek SBC formájában , általában Linux- tal ( Debian , Fedora , Ubuntu , Yocto ) vagy akár az OpenWrt változataival , szerverekkel és egy 2019-ben elindított európai projekttel, célja, hogy hazai szuperszámítógépekben gyorsítóként használják alacsony - az erőteljes SoC-k lokálisan fejlődtek és GNU / Linux alatt futottak , mint a szuperszámítógépek túlnyomó többsége.

Motivációk

Ezt a projektet, amelyet eredetileg a Kaliforniai Egyetem, Berkeley , Amerikai Egyesült Államok informatikai részlegében hozták létre, eredetileg tanulmányokra és kutatásra szánták, de de facto az ipar nyílt architektúrájának szabványává vált.

A projekt célja a mikroprocesszoros utasításkészlet nyílt szabványának elkészítése, például a hálózatok TCP / IP szabványa vagy az operációs rendszerek UNIX rendszere, a processzorok architektúrája jelenleg mindig zárva van, korlátozva az előrehaladást, az operációs rendszerek megvalósítását vagy támogatását .

Történelmi

A processzor tervezése 2010-ben kezdődik a Berkeley-i Kaliforniai Egyetemen, annak érdekében, hogy olyan processzort fejlesszenek ki, amely ismeri a XXI . Századot , és nem kell a régi architektúrákkal való kompatibilitást 20 évig húzni, mint az ARM vagy az Intel x86 - os architektúrája, és ugyanakkor a processzor utasításkészlet (ISA) architektúra nyitva maradása.

2014-ben a specifikációk 2.0 verziója jelent meg, több nagy gyártó is érdeklődött a projekt iránt.

2015-ben létrejött a RISC-V alapítvány több mint 100 taggal, valamint az igazgatóság, amely olyan vállalatokból állt, mint a Google , az Nvidia , a Western Digital , az NXP Semiconductors , a Microsemi és a Bluespec , valamint a University of University képviselői. Berkeley. Azóta olyan vállalatok csatlakoztak, mint az AMD , a Qualcomm és az IBM .

2016-ban az Nvidia egy RISC-V mikrovezérlő használatát tervezi GPU-jához, és így a saját mikrovezérlőjéhez, a Falconhoz képest a teljesítményének megháromszorozására számít. A Falcon is egy RISC architektúrán processzor, de korlátozott 32 bites címzési és nincs menet védelmet és a korlátai. Az Nvidia ezért le akarja cserélni a RISC-V 64 bites változatára, így profitálva a 64 bites címzésből, a hibajavításokból, a bővíthető utasításkészletből és a jobb biztonságból.

2017-ben megjelent a specifikációk 2.2-es verziója. A Mozilla bejelenti, hogy Rust nyelve összeállítható a RISC-V architektúrával. A merevlemezek gyártója, a Western Digital bejelenti, hogy milliárdnyi berendezését szállítja RISC-V vezérlő architektúrával.

az 2018. július 9, az ARM vállalat vezetésének egy része úgy dönt, hogy létrehoz egy „riscv-basics.com” nevű weboldalt a RISC-V ellen, veszélyeztetettnek érezve a piacát, különösen azért, mert a legnagyobb (fent említett) ügyfeleinek jelentős része is a RISC-V alapú megoldások fejlesztésének megkezdése. Ez az akció feldühítette a vállalat technikai személyzetét, aki a nyílt forráskódú mozgalom elleni támadásként tekintett rá. Ennek az a hatása is, hogy egy kicsit jobban felhívja a figyelmet a RISC-V-re, és nagyobb tudatosságot teremt arról, hogy ez életképes alternatíva. Az ARM vezetése végül úgy dönt, hogy másnap bezárja az oldalt, aJúlius 10 2018.

2019-ben Donald Trump amerikai kormánya nyomást gyakorol a mikroelektronika alapítóira, például a tajvani TSMC-re , amely a világ legfontosabb, hogy költözzenek az amerikai földre, amelyet utóbbi nem hajlandó elutasítani, mindezt azzal fenyegetve, hogy továbbra is dolgozzon olyan kínai vállalatokkal, mint a Huawei . E nyomások politikai kockázatait követve az Alapítvány úgy döntött, hogy egy semleges országban, Svájcban telepedik le .

Ban ben 2019. október, Az Nvidia RISC-V szakembereket keres, hogy processzorként integrálják a Tegra SoC-be .

Ban ben 2020 október, A Huawei kiadja első belső hardver- és szoftverfejlesztő készletét új házon belüli mikrovezérlőihez, és fordítót használnak a RISC-V architektúra felé.

Ban ben 2021. július, Haiku a RISC-V-be van portolva, a Debian Bulleseye szolgáltatás befagyasztása a disztribúció első verziójának kiadásához, amely hivatalosan támogatja a RISC-V-t. A Radeon HD grafikus illesztőprogram Linux rendszerhez fut.

Specifikációk

Ez megvalósítja a RISC utasításkészlet nélkül mikrokód , sem overlay építészet típusú végrehajtás a betegség , vagy a sorrendben, illetve a támogatást a típusú anyag különösen ( ASIC , FPGA ...), de azok -ci lehet végrehajtani minden funkciójukkal.

- Az IEEE-754 szabvány 2008. évi felülvizsgálata a lebegőpontos számok kiszámításához .

- 32, 64 vagy 128 bites címzés.

- Minden megvalósítás lehetősége kiterjesztett utasítások megadására.

- Támogatás a rendkívül párhuzamos többmagos megvalósításhoz és a heterogén többprocesszoros architektúrához.

- Opcionális változó hosszúságú utasítások, amelyek lehetővé teszik mind a rendelkezésre álló utasításkódolási hely növelését, mind pedig az utasítások sűrűbbé tételét a teljesítmény javítása, a statikus kódméret csökkentése és a hatékonyság energikusabbá tétele érdekében.

- Teljesen virtualizálható architektúra a hipervizor fejlesztésének megkönnyítésére .

A kaliforniai Berkeley Egyetem kutatói szintén kifejlesztették a BOOM nevű verziót, amely az utasítások rendelésen kívüli végrehajtását egészíti ki az RV64G modellben.

A kiterjesztés nómenklatúrája

A processzor nevének jelentése:

- Az alapot RV alkotja (RISC-V esetén), majd 32, 64 vagy 128, a bitek számától függően, végül egy I vagy E (beágyazott, vagyis beágyazott).

A lehetséges alapnevek tehát:

- RV32I

- RV32E (fedélzeti)

- RV64I

- RV128I

A processzor nevét egy vagy több betű követi, amelyek leírják az adatbázishoz hozzáadott kiterjesztéseket:

- M - Standard kiterjesztés m ultiplikációk és egész osztások;

- A - A standard utasítás kiterjesztésnek vannak tomikumai ;

- F - standard precíziós lebegőpontos f kiterjesztés (32 bit);

- D - szabványos lebegőpontos Extension d ouble pontosságú (64 bit);

- G - G eneral, rövidítés az alapvető utasításokhoz, és a fenti utasításkészletek, azaz M, A, F, D)

- Q - normál q háromszoros precíziós (128 bites) lebegőpontos kiterjesztés ;

- L - szokásos lebegőpontos kiterjesztés, tizedelte a ;

- C - Standard Instruction Extension c ompressées;

- B - Normál manipuláció Bővítés b ict;

- J - A dinamikusan lefordított nyelvek szabványos kiterjesztése ( Összeállítás menet közben , J ust in time vagy JIT), ez olyan szkriptnyelvekre vonatkozik, mint a C # , Haskell , Java , JavaScript , Lua , OCaml , PHP , Python , R , Ruby , Scala , WebAssembly stb .;

- T - Standard memóriabővítmény t ransactionnelle;

- P - a standard utasítás kiterjesztés SIMD com p leírása ( P acked SIMD );

- V - Normál meghosszabbítása műveletek v ectorielles ;

- N - szabvány kiterjesztése i n felhasználói terruptions;

- S - az S upervisor szabványos kiterjesztése ;

- H - Standard H ypervisor kiterjesztés , hasonló az S-hez, de S-vel kezdődik.

Alapvető 32 bites ISA

Az alapvető utasításkészlet alkotják 47 utasításokat, köztük nyolc rendszer utasításait (rendszer kéri , kivitelezés számlálók), a többi van osztva kategóriák számítás, flow control és memória-hozzáférést.

az RV32I verzió 32 32 bites általános regisztert tartalmaz, míg az RV32E verzió (fedélzeti, beágyazott ) csak 16 32 bites általános regisztert tartalmaz. Mindkettő rendelkezik PC-regisztrációval is.

Számítási utasításokAz összes számítási utasítás három operandust használ, kivéve azokat lui, auipcamelyeknek csak kettő van (célregiszter és azonnali érték). Az első operandus a célregiszter, a második a forrásregiszter és a harmadik, vagy egy második regiszter, vagy egy azonnali érték (amelyet iaz utasítás mnemonikájában egy a határoz meg , kivéve, auipcha más jelentése van) (A szorzási utasításokat és osztási egész számokat a M kiterjesztés):

- add, addi, sub : Összeadás és kivonás addi használjuk negatív közvetlen értéket a kivonás az azonnali értéket.

- sll, slli, srl, srli, sra, srai : Biteltolás bit ( ek hift ) + bal / jobb ( en), a logika ( l ogical ) vagy aritmetikai ( a rithmetic ).

- and, andi, or, ori, xor, xori : Logikai műveletek Bitorientált beleértve és ( és ), vagy ( arany ) és kizárólagos VAGY ( XOR ).

- slt, slti, sltu, sltui, ( S , és amennyiben az ESS t han ) beállítja a rendeltetési regiszter 1, ha az első forrás operandus egyenlő vagy kisebb, mint a második. Aláíratlan u jelző ( u njelzett ). Azonnali operandusok 12 bitre korlátozódnak.

- lui, Betölti a legjelentősebb közvetlen rész ( l OAD u pper i mmediate ), azaz bitek 12-31 a cél regiszter azonnali 20 bites érték. Az addiértéket azonnali 12 bites értékkel kell használni .

- auipchozzáadja a közvetlen értéket a sorszámláló (PC) 20 legjelentősebb bitjéhezaddi , a 12 legkevésbé jelentős bithez is fel kell használni

Feltételes elágazási utasítás:

- beq, bne, blt, bltu, bge, bgeu, Instruction ág ( b Ranch ) feltételes a két szolgáltató rész, amely azonos ( e minő ), a különböző ( n OT e minő ), kisebb ( a ittler t han ), nagyobb, mint vagy egyenlő ( g reater arany e minő ) aláírt (alapértelmezett) vagy nem ( u nsigned ).

Feltétel nélküli kapcsolatok:

- jal( J UMP egy nd l festék ), átadja a vezérlést a címet a PC, amely hozzáadódik a közvetlen 20 bites előjeles érték biztosított. Hozzáadja a következő utasítás címét (visszatérési cím a meghívott függvény végén) a célregiszterbe.

- jalr( J UMP egy nd l tinta, r egister ), a folytatásban cím összeadásával számítják a forrás regiszter és a közvetlen 12 bites érték, és az utasítás címét betöltődik a cél. Ha ezt az utasítást auipc parancs előzi meg, az ugrás a teljes 32 bites memóriaterületen végrehajtható.

A memória-hozzáférési utasítások az adatok átvitelére szolgálnak egy regiszter és a memória között. Az első operandus a regiszter, a második a címet tartalmazó regiszter, a harmadik a címzéshez használt regiszter tartalmához hozzáadott 12 bites azonnali érték a végső cím meghatározása érdekében:

- lb, lbu, lh, lhu, lw, Betöltése ( l OAD ) egy byte ( b YTE ), halfword ( h ALF-szót , 16-bites) vagy szó ( w ORD , 32 bit) a memóriából, hogy a cél regiszter. Az utasítások meghosszabbította a jel (alapértelmezett) vagy nulla ( u nsigned ).

- sb, sh, sw, Tárolás ( s tórusz ), egy byte ( b YTE ), halfword ( h ALF-szót , 16-bites) vagy szó ( w ORD , 32 bit), hogy a memóriát.

- fence, kényszeríti a memória-hozzáférés ütemezését többszálas kontextusban, különösen a gyorsítótárak konzisztenciájának biztosításával.

- fence.i, lehetővé teszi, hogy a műveletek a tárolástól az utasításmemóriákig (például az utasítások gyorsítótáráig) befejeződjenek a végrehajtás előtt. Főleg önállóan módosított kód esetén alkalmazzák.

Az egyik utasítás a rendszerhívás meghívására szolgál , a másik pedig töréspontot állít be a hibakereső számára :

- ecall, rendszerhívás

- break, töréspont hozzáadásával.

Hat utasítással olvasható és írható a rendszer vezérlő és állapotregisztereibe ( vezérlő és állapotregiszterek CSR). A CSR-nyilvántartást egy általános regiszterben olvassák el, majd atomikusan frissítik:

- csrrw, csrrwi, csrrc, csrrci, csrrs, csrrsi,

A következő 6 32 bites CSR regisztráció (amely 3 64 bites értéknek felel meg a végrehajtási számlálóknál) csak olvashatóként definiálva van:

- cycle,, A cyclehciklusszámlálók egy referenciaidő óta elteltek. Ez az idő változhat, ha a dinamikus feszültség és frekvencia méretezés (DVFS) mód aktív;

- time,, timehValós idejű számláló eltelt egy referenciaidő óta (általában a rendszer indításakor);

- instret, instrethCounter processzor végrehajtott utasítások ( Inst kalamajka ret IRED ).

Alapvető 64 bites ISA

A 64 bites ISA kiterjeszti a regisztereket és a címteret 32 bitesről 64 bitesre (XLEN = 64). A W utótaggal ellátott utasítások ( angolul : W ord , szó jelentése ) azt jelzik, hogy a műveletük egy szóra (32 bit) korlátozódik, és nem foglalkoznak a bemenetek felső 32 bitjével. Az aláíró bit áthelyezésre kerül a regiszterek 64. bitjére (63. bit), ezért fontos a speciális funkciók használata 32 bites adatok használatakor.

Ez kihat a közvetlen műveletekre is. Például az addi azonnali összeadási művelet azonnali 12 bites érték felhasználásával, az addiw figyelmen kívül hagyja a 32 bites túlcsordulásokat, és az előjelbitet a regiszterek 63. bitjére helyezi.

Alapvető 128 bites ISA

Vektor kiterjesztés

A vektor kiterjesztésnek három változója van: ELEN (egy elem bitjeinek száma), VLEN (egy vektor bitjeinek száma) és SLEN (két elem közötti (csíkolás) távolsága), amelyeknek mind 2-nek kell lenniük.

Ez magában foglalja a 32 vektorregiszterrel elemzi a V0 v31, lehetőség van a második csoport, milyen az úgynevezett csoport vektor regiszter ( vektor regiszter csoport ), hogy javítsa a pontosság vagy teljesítmény javítása érdekében. Ezenkívül hat Control and Status ( CSR) regiszter is létezik (vstart, vxsat, vxrm, vtype, vl, vlenb).

GPU

RV64X GPUEgy munkacsoport javasolja 2021. januáregy RV64X nevű GPU kiterjesztés, amely elsősorban a vektorprocesszor kiterjesztésén és a Libre GPU projekt által javasolt VBlock formátumon alapul, amely ASIC vagy FPGA formátumban valósítható meg. Az első verzió célja a Khronos Vulkan API-val kompatibilis illesztőprogram használata , hogy később támogassa az OpenGL-t és a Direct3D-t . Kezdetben a fedélzet területére is vonatkoznia kell. A megszorítások a következők:

- 64 bites utasítás;

- Támogatás a komplex függvények sin , cos , atan , pow , exp , log , rcp RSQ, sqrt , stb

- Of vektorok hordozó 2-4 elemek 8, 16 vagy 32 bit;

- Of mátrixok tér 2 × 2, 3 × 3 és 4 × 4;

- pixelek 8, 16, 32 és 64 bites formátumban;

- A pontok 4 dimenzióban XYZW, 64 vagy 128 bit;

- A pixelek 4 RVGA komponensek, 8, 16, 24 vagy 32 bit komponenst;

- A texels UVW 3 komponensekkel rendelkezik, 8 vagy 16 bit;

- Támogatja a fényváltozókat, Ia, ka, Id, kd, Is, ks ...

Ban ben 2019 december, a Think Sillicon vállalat a RISC-V architektúrán alapuló GPU-t javasolt.

Egy másik RISC-V alapú GPU megszakadt2018-ban a kazan vagy a Libre RISC-V projekt célja a RISC-V alapú GPU fejlesztése volt. 2020-ban, mivel a különböző nézeteltérések működésének RISC-V alapítvány, a szerzők a projekt Reorient magát egy OpenPower építészet, a nyílt változata teljesítmény , a RISC architektúra az 1990-es évek származó IBM , A szerzők végül pedig a teremtés egy SV processzor kiterjesztésű Power processzor kiterjesztés, amely közel áll a RISC-V V kiterjesztéséhez, és nem GPU fejlesztése.

Szoftvertámogatás

Ezen architektúra fejlesztésére számos ingyenes eszközt javasolnak, ideértve a GCC és az LLVM fordítók (tehát a Clang ) kompatibilitását, a GDB hibakereső , valamint a QEMU hipervizor és emulátor támogatását . A Rust nyelv azóta támogatja a RISC-V-t 2017. november.

A assembler szinten , GNU Assembler támogatja a 32 és 64 bites RISC-V architektúrák (assembler, disassembler), és riscv-assembler egy assembler a Python .

A Bronzebeard egy RV32IMAC összeszerelő, amelyet Python iratgyűjtő programban írtak össze egy minimalista könyvtárban, hogy biztosítsa a csupasz fém (In) rendszerét . Először a Sipeed, a Longan Nano és a Wio Lite kártyáin, valamint a GigaDevice GD32V processzorán tesztelték, mivel az a lehetőség, hogy a képernyőjével könnyebben hozzáférhessen az ilyen típusú anyagokhoz kevesebb, mint 10 euróért. A szerző azt tervezi, hogy a HiFive1 Rev B-be is továbbítja, ugyanez a szerző készített egy Forth csupasz fém tolmácsot is a RISC-V-hez.

Ezt az architektúrát a 2016. januára Linux kernel javítások segítségével, valamint a FreeBSD. Integrációja a stabil Linux magba a 4.15-ös verzió óta hatékony, a 4.17-es verzió óta szélesebb körű támogatással.

A MicroPython szkriptnyelvet , a Python mikrovezérlőkhöz igazított verziót 2017-ben a Microsemi a RISC-V architektúrába hordozta .

Arduino fut GD32V mikrokontroller származó GigaDevice . Ehhez használhatja az RT-Thread valós idejű rendszert és az Arduino RTT-GUI grafikus felületét .

A Zephyr valós idejű rendszer a RISC-V processzorokon is működik, különösen a Qemu általi emuláción és különféle hardveres megvalósításokon.

A beágyazott Rust minimális verzióját (Minimum Supported Rust Version (MSRV)) a RISC-V-be portolja a rozsdába ágyazott közösség. Az rCore rendszermagra épülő RustOS rendszer, az uCore OS Plus Rust verziója a RISC-V Qemu megvalósításán és a HiFive Unleashed rendszereken fut, és a Tsinghua Egyetemen használják operációs rendszer órákra.

Az UltraSOC vállalat kifejlesztette a "Tessent Embedded Analytics" elemzési és nyomonkövetési megoldást a RISC-V-en, saját vagy nyílt megoldásokhoz. A Siemens csoport vásárolta meg, és folytatja ezt a tevékenységet a csoporton belül.

Ezt az architektúrát a tárgyak internete , a LiteOS (BSD licenc) és a Huawei HarmonyOS mobilplatformjainak operációs rendszerei támogatják .

A szoftver segít felfedezni a biztonsági réseket, annak érdekében, hogy képes legyen kihasználni őket, az Egyesült Államok hírszerző szolgálat , NSA , Ghidra , támogatja a bináris formátumú e építészet.

Ban ben 2020 január, Alibaba bizonyítja Android 10 által átvitt T-Head azok ICE EVB SoC jellemző 2 XuanTie C910 64 bites RISC-V magok, egy XuanTie C910V vektort magot és egy GC8000UL Élő GPU .

Szerverek és asztali gépek operációs rendszerei

Különböző Linux disztribúciók érhetők el, beleértve a Debian Bullseye portált csomagok több mint 95% -át, Fedora , Ubuntu , Yocto . A FreeBSD és a Haiku operációs rendszerek a RISC-V rendszeren is elindulnak.

A Linux és a Haiku élvezheti az AMD Radeon HD grafikus kártyák gyorsítását az ingyenes Mesa meghajtón keresztül, amely független a processzor architektúrájától.

Szoftver emulátorok

Ezeket az architektúrákat különböző emulátorok és hipervizorok segítségével lehet szimulálni.

A QEMU hipervizor , valamint az ANGEL (egy RISC-V szimulátor HTML5-ben és JavaScript-ben ), vagy a Xilinx Zynq FPGA-kat tartalmazó ZedBoard és Zybo kártyákon keresztül . A RISC-V emulációt (32 és 64 bit) natív módon támogatja a Qemu a 2.12.0 verziótól 2018. április 24. Az 5.1-es verzió támogatja a bios kiválasztását az argumentumokban.

TinyEMU által Fabrice Bellard (is szerzője QEMU és ffmpeg ) könnyű RISC-V emulátor, akkor használjuk a kikötő Haiku (ingyenes remake BeOS ). Azt is használják BareDoom, kikötőben Doom RISC-V keresztül Barebox ez a változata TinyEMU maga pedig recompiled a WebAssembly (WASM) futtatni a böngészőben.

A Juice-VM egy minimalista RISC-V RV64IMASU virtuális gép-emulátor , amely támogatja az MMU-t és az UART I / O-t. Lehetővé teszi a FreeRTOS futtatását, valamint a nagyon korlátozott erőforrásokkal rendelkező rendszereken, például a kétmagos ESP32 Xtensa típusú mikrovezérlőkön 8 MB PSRAM-mal és 2 MB SPI flash-rel, a Linux 5.0 rendszermaggal, amelyet a RISC-V architektúrához állítottak össze.

A RISC-V Rust egy RISC-V emulátor, amelyet Rust nyelven fejlesztettek ki, és a WebAssembly-ben fut. A cél az emulátor használata egy böngészőben. GNU / Linux és xv6 -riscv operációs rendszerek működnek rajta.

Hardver implementációk

fejlesztési eszközök

A Wrap-V egy RISC-V maggenerátor, amely támogatja a TL-Verilog (Transaction-Level Verilog ) MIPS architektúráját és áthalad az M4 makroprocesszoron . Lehetővé teszi olyan magok kifejlesztését, amelyek csővezetékei 1–7 szinttel rendelkeznek. Lehetőség van az M4 kimenet módosítására, hogy az a speciális igényekhez igazodjon. Lehetőség van a TL-Chisel használatára is .

Ingyenes megvalósítások

Az ingyenes LowRISC mikroprocesszor a RISC-V ingyenes és nyílt megvalósítási projektje, amelyet Andrew Huang (az MIT-től , a Novena nyílt platform szerzője is ), Julius Baxter ( OpenRISC projekt és Cambridge-i Egyetem ), Michael B. Taylor ( Egyetem) hozott létre. of California, San Diego , UCSD Központ Sötét Silicon), Dominic Rizzo ( Google atap (en) ), Krste Asanović ( University of California, Berkeley ).

A NEORV32 egy platformfüggetlen mikrokontroller típusú SoC for FPGA-k VHDL-ben írt ingyenes implementációja ( BSD licenccikk 3. pont). Kompatibilis az RV32 RISC-V 2.2 specifikációjával, és megfelel a megfelelőségi tesztnek. A FreeRTOS -t erre a SoC-re portálták . Azon a munkán alapul, amelyet a fejlesztőknek a neo430-on kellett végrehajtaniuk, amely egy olyan mikro típusú FPGA processzor megvalósítása, amely kompatibilis a Texas Instruments MSP430- mal .

A PicoRV32 egy ingyenes, ISC licenc alapján megvalósított megvalósítás, amely támogatja az RV32IMC utasításkészleteket, amelyek célja a lehető legkisebb alapterület biztosítása, 750 és 2000 LUT közötti választással és 250–450 MHz maximális frekvenciával. Célja egy FPGA vagy ASIC kiegészítő processzorának lenni. Konfigurálható RV32E, RV32I, RV32IC, RV32IM vagy RV32IMC magként (lásd a #Bővítmények nomenklatúrája részt ).

A Western Digital a SweRV nevű, nyílt forráskódú, a CHIP Alliance-on keresztül elérhető magválasztékot kínálja. Bejelentették az együttműködést a Codasip-szel is annak érdekében, hogy kereskedelmi támogatást nyújtsanak ezeknek a szíveknek. Ezek a nagy teljesítményű processzorok beágyazott tartományokra irányulnak, és támogatják az RV32IMC utasításkészletet. A SweRV család a következőképpen oszlik fel:

- A SweRV EH1 Superscalar Core 2 végrehajtási sorral rendelkezik, és egy 9 fokozatú vezetékre épül.

- A SweRV EH2 többszálú szuperkalár mag 2 szálat képes egyszerre kezelni 9 csővezeték szakaszával.

- A SweRV EL2 mag egyetlen kivezetése 4 csővezeték fokozattal.

A Kínai Tudományos Akadémia kiadta a Xiangshan processzor mellett egy szabad licenc ( Mulan v2 licenc , OSI jóváhagyott ) szóló2021. június 11a Githubon . A processzort Chisel nyelven fejlesztették ki , amely a fejlesztők szerint ötször kevesebb kódsorral rendelkezik, mint a Verilog, és gyorsabb fejlesztést tesz lehetővé. A megjelenéskor a processzor támogatja a Debian Bulleseye disztribúciót a RISC-V számára. Az első hardveres megvalósítás megjelenik2021. július, Yanqihu néven, bevésve 28 nm-re, frekvenciája 1,2 és 1,3 GHz között van, GHz-es teljesítménye hasonló az ARM Cortex-A72-hez , 7 / Ghz SPEC CPU 2006 - mal. Ugyanezen év őszére tervezett második verzió, Nanhu, bevésve 14 GHz-en és 2 GHz-en működik, el kell érnie GHz-enkénti teljesítményét, hasonlóan az Intel i9-10900K (11,08 / Ghz) 10 / Ghz SPEC CPU 2006-hoz, és ezen a frekvencián az ARM Cortex- A76 .

Saját RISC-V megvalósítások

SiFive, egy startup bejelenti 2016. júliusA SiFive U5 Coreplex segítségével RISC-V építészet és beültetésére U54 akár nyolc maggal SoC , amelyek mindegyike tartalmaz utasítás cache és az adatok a 1 st szinten, a SoC tartalmaz egy nagyobb cache 2 e szinten. A cél az lesz, hogy először olyan verziókat vezessenek be olyan nagyon specifikus hardverekhez, amelyekhez nem kell sok energia, de először speciális funkciókra van szükség, hogy később képesek legyenek fejleszteni a technológiákat.

2018-ban a RISC-V fejlesztői által létrehozott SiFive startup a FOSDEM-en bemutatta a HiFive Unleashed kártyát , amely egy SiFive Freedom U540 SoC processzort (4 + 1 RISC-V mag 1,5 GHz-ig) és 8 Gio ECC RAM-ot tartalmaz, Gb Ethernet port, és képes a GNU / Linux futtatására .

A Shakti egy indiai kezdeményezés különböző processzorok tervezésére, amelyek a RISC-V architektúrán alapulnak és 6 sorozatra tagolódnak: E-osztály beágyazotthoz, C-osztály mikrovezérlőkhöz, I-osztály mikroprocesszorokhoz vékony kliensekhez, M -osztály irodai automatizáláshoz , S-osztály munkaállomásokhoz és szerverekhez, végül H-osztály szuperszámítógépekhez.

A Codasip az első vállalat, amely kifejlesztett egy nem szabad RISC-V kompatibilis magot 2016. január(Codix), és folytatta kínálatát a magcsaládokkal beágyazott és alkalmazási területekre. A Codasip által kifejlesztett magok a CodAL, egy építészeti leíró nyelvvel vannak megírva. A Studio eszköz a szimulátorok, valamint az ezen magok fizikai megvalósításához szükséges fájlok beszerzésére szolgál.

Az L család egyesíti az alacsony fogyasztású 32 bites magokat, fedélzeti tartományokat céloz meg, és opcionális lebegőpontos számítási egységet kínál. Ez a család 3 vagy 5 csővezeték szakaszban áll rendelkezésre.

A H család egyesíti a nagy teljesítményű 64 bites magokat, amelyek a fedélzeti domaineket célozzák, és opcióként egy lebegő számítási egységet kínál.

Az A család 64 bites mag, amely képes futtatni a Linuxot, azzal a lehetőséggel, hogy kibővítse őket a „P” kiterjesztéssel. Ezeknek a magoknak 7 csővezeték szakasza van, egy lebegő számítási egység, egy MMU. Ezenkívül az -MP verziók integrálják az 1. (L1) és a 2. (L2) szintű gyorsítótárat, és fürtönként legfeljebb 4 magot támogatnak.

A Codasip Studióban elérhetővé tett uRISC-V magot tanulásra vagy tesztelésre szánják.

Beágyazott és mikrokontrollerek

A 7 -én RISC-V Műhely , Western Digital bejelentette, hogy a vállalat fejlesztésére RISC-V processzorok. A Western Digital célja átmenet megkezdése nyílt forráskódú megoldásokra a tárolószervereihez. Végül a WD évente csaknem kétmilliárd RISC-V processzor eladására számít.

2018-ban a Grenoble-alapú startable fabless GreenWave bemutatta a mesterséges intelligenciára optimalizált GAP8-at, az IoT alacsony fogyasztású processzorát .

2019-ben a GigaDevice Semiconductor elindítja a GD32V mikrovezérlők sorozatát, az architektúra 32 bites verziója alapján. A 14 verzió közül a GD32VF103 108 MHz-es órajelű, és integrált flash memóriájába várakozási állapotok (in) nélkül, tehát késés nélkül fér hozzá . 128 KiB chip-es flash memóriával és 32 KiB SRAM-mal , 2 db 12 bites analóg-digitális és 2 db 12 bites digitális – analóg átalakítóval, valamint különféle kommunikációs interfészekkel rendelkezik (3 SPI, 2 I2C , 3 USART, 2 UART, 2 I2S, 2 CAN és 1 USB OTG). A chip pin-to-pin kompatibilis az ARM architektúrán alapuló GD32 mikrovezérlőivel , valamint az STMicroelectronics STM32 - ével , megkönnyítve ezzel az alkalmazások egyik architektúráról a másikra történő áthelyezését , valamint Arduino kompatibilitását is . A GD32V-ket különösen a Sipeed Longan Nano fejlesztõ táblában használják .

A Sipeed kifejlesztette a Sipeed M1 (vagy Kendryte KD233) kártyát is, amely 2 64 bites RISC-V magot és mesterséges intelligencia processzort tartalmazó Kendryte K210 SoC- val van felszerelve . Ezeket a kártyákat úgy tervezték, hogy működjenek a FreeRTOS-szal . Ez a kártya a MAIXPy-t használja, a MicroPython megfelelő verzióját, amely a Plateform.IO-n keresztül programozható. Különböző variációk léteznek, mint például MaixDuino , akinek kártya egy kompatibilis formátumban Arduino , és támogatja az IDE. Linux operációs rendszerrel is használható . Más, kompaktabb verziók is kaphatók. Ban ben2021. július A Canaan kiadta a továbbfejlesztett verziót, a Kendryte K510-et, amely egy 2 RV64 magból álló mikroprocesszoros részt és egy másik DSP kiterjesztésű RV64-ből álló gyorsítót tartalmaz.

2019-ben az Egyesült Államok elnöke, Donald Trump azzal fenyeget, hogy blokkolja a Huawei beszállítóit, köztük olyan alapítókat, mint a TMSC, és a brit ARM vállalatot, amely addig biztosította a HiSilicon processzorokban használt magok IP- jét . A Huawei-től. Az amerikai Nvidia vállalat, miután megvásárolta az ARM vállalat jogait a japán SoftBanktól , a Huawei-nek meg kellett találnia a megoldást, és úgy tűnik, hogy a RISC-V-hez fordult. Az első HiHope HiSpark Wifi IoT fejlesztőkészletek egy Hisilicon Hi3518 mikrovezérlőt használnak, amely kompatibilis az új platformjaival, a Huawei LiteOS-szal és a HarmonyOS-szal . A mellékelt fordítók GCC fordítók 32 bites RISC-V architektúra kódok számára.

Ban ben 2021. július, Az Espressif bejelenti egy új NodeMCU modell elérhetőségét, amely az ESP32-C3 processzorra épül, a RISC-V architektúrára.

Hálózati modulokOpenWifi , bemutatva2019 december, egy nyílt forráskódú, Linux kompatibilis WiFi verem, amely FPGA-n futtatható. Funkcionális megvalósítás történt az Xilinx FPGA-n, amely fmcomms2 / fmcomms4 RF kártyához csatlakozik

A Bouffalo Lab BL602 / BL604 moduljai, amelyek 32 bites RISC-V-n alapulnak, WiFi és Bluetooth 5.0 LE modulok. A Sipeed és a Pine64 integrálja őket az IoT térképeibe.

Ban ben 2020 november, Az Espressif bejelenti az ESP32-C3, a WiFi & BLE , az ESP32 -vel összhangban lévő , de az ESP8266-tal pin-to-pin kompatibilis processzor megjelenését , és 32 bites RISC-V architektúrát használ az Xtensa LX6 helyett. Kriptográfiai processzorral rendelkezik, de az ESP32-vel ellentétben nincs DSP.

HelyAz európai űrügynökség az NOA-V nevű neurális processzort fejleszti, amely az ISA RISC-V és annak vektor kiterjesztése (V vagy RVVE) alapján RHBD (Radiation Hardened By Design) technológiát alkalmaz, az űrkörnyezet korlátai miatt ( hőmérséklet és ionizáló sugarak), valamint az energiahatékonysági korlátok a műholdak középpontjában. A projektet Cobham Gaisler vezeti az Európai Űrkutatási és Technológiai Központban (ESTEC), aki már 2019-ben gyártott egy hasonló LEON nevű processzort, amely az 1990-es évek végén a SPARC- V8 architektúrán alapult .

KülönféleA Pine64 Pinecil egy elektronikusan szabályozott forrasztópáka, amely 108 MHz - es RISC-V RV32IMAC " Bumblebee Core " processzoron alapszik .

A Sipeed RV-Debugger Plus egy nyílt forráskódú UART csatlakozó (soros) és JTAG hibakereső , amely a Bouffalo Lab BL702 SoC-n alapul, 32 bites, 144 MHz-es RISC-V mikrovezérlőt használva, amely FPU-t, titkosító modult, Audio (I2S) tartalmaz. master / slave), a Zigbee 6-ot, a Bluetooth 5.0 LE-t, a WiFi-t és az internetet kezeli. A firmware ingyenes szoftver , fejlesztői fórumként is használható.

FPGA

ZedBoard és Zybo jellemző Xilinx FPGA .

A (z) LicheePi ingyenes anyagtérképe, a LicheeTang2018. szeptember, egy kártya, amely egy RISC-V architektúrán alapuló mikrokontrollert és egy FPGA-t használ, egy Anlogic EG4S20- at használ. Ez GPIOs az érdekében, hogy képes legyen csatlakozni a különböző típusú elektronikus elemekkel gazdagítják.

A Tang Nano FPGA board , bemutatott2019. október, a Sipeed cégtől, a LittleBee családjának GOWIN Semi GW1N FPGA- ját használja .

A Hummingbird E200 (vagy HBird E200) processzormagsor a RISC-V nyílt forráskódú kínai megvalósítása, és FPGA implementációkat tartalmaz .

Ban ben 2019 december, Az OpenWiFi bemutatásra kerül. Ez egy ingyenes hardveres és szoftveres WiFi-verem, amely FPGA-n fut, és implementációval rendelkezik a Xilinx-en.

Ban ben 2020. június, Az Efinix 3 RISCV32I 32 bites architektúrát kínál a Trion FPGA-ra optimalizálva

Ban ben 2020 július, bemutatja a PolarFire 64 bites SOC alapú nyílt forráskódú SAVVY-V kártyát . A PolarFire SoC Icicle egy FPGA SoC-t használ 5 64 bites maggal, köztük egy RV64IMAC és négy RV64GC-vel, és 2 GiB LPDDR4 RAM-mal felszerelve.2019 decemberVégül megjelent a 3 -én félév 2020. PolarBerry is javasolják crawdfunding variáns2020 október.

SBC

Különböző típusú SBC táblák, és Linux operációs rendszert futtató, kerülnek bemutatásra 2018. próbálják meg az árát hasonlít a népszerű Raspberry Pi : A SBC HiFive póráz (hu) kerül bemutatásra2018. február, négy U54 RV64GC (64 bites) 1,5 GHz-es magot és 8 GiB DDR4- típusú ECC RAM-ot tartalmazó SoC-n alapul, tömeges finanszírozás alapján.

Az Imagination Technologies és a RISC-V International Open Source (RIOS) laboratórium összeállt, hogy egy SBC- típusú kártya úgynevezett PicoRio , leleplezett2020 szeptembera RISC-V Globális Fórumon a platform általában nyílt forráskódú, kivéve bizonyos lényeges részeket, mint például az I / O vagy a memória hozzáférés.

Ban ben 2020 november, A Sipeed bejelenti egy SBC-t egy AllWinner , egymagos SoC használatával , amely egy XuanTie C906 (RV64GCV) 1 GHz-es, 22 nm-es frekvencián áll, és amelyet a 16 magos RISC-V 64 bites processzor, az Alibaba XT910 tervezői készítettek. it n nincs 3D GPU-ja, de van 2D-s GPU, és egy hardveres videodekóder, H.264 és H.265, 64 MiB-tól 256 MiB-ig forrasztott RAM-ig (és egyes modelleknél külső RAM is lehet), valamint HDMI, Gb Ethernet, USB és USB OTG kapcsolatok

Ban ben 2021. január, Az SBC egy SoC BeagleV StarFive JH7100-at használ, amely egy RISC-V processzoros dupla szívű SiFive U74-et, egy DSP DSP Vision Tensilica-VP6-ot, egy motoros NVDLA-t (nyílt architektúra NVIDIA Deep Learning Accelerator) és egy neurális hálózati motort használ az AI gyorsításához. Első verziója nem rendelkezik 3D geometriai processzorral, a második verzió az Imagination Technologies GPU- ját fogja tartalmazni (ezért nyitott illesztőprogram nélkül). Végül a SoC tartalmaz egy VPU-t, amely képes a H.264 és a H.265 dekódolására 4Kp60-ig, vagy két adatfolyamot 2Kp30-ban. A kártya 4 vagy 8 GB RAM-mal rendelkezik LPDDR4-ben, 4 USB 3.0-porttal, 10 Gb-os Ethernet- porttal , HDMI 2.0, DSI-vel, két ISP-vel, 40 tűs porttal és USB-C tápellátással. Két változat érhető el, az egyik 4 GB RAM-mal 100 dollárért, a másik pedig 8 GB-os 150 dollárért. A TSMC által 7 nm-es vésett processzorok 3,5 GHz-en működnek, és RV64GCVBH típusúak (különösen vektoros egységgel) és egy processzor teljesítményt ér el az ARM Cortex-A76 és A77 készülékeken . Ban ben2021. május, a Fedora disztribúciót javasoljuk alapértelmezett terjesztésként, az első térképek a fejlesztők rendelkezésére állnak. Az XFCE az alapértelmezett ablakkezelő, amely megjeleníthető a HDMI kimeneten.

Ban ben 2021. februárA Pine64 bejelentette az RV64GCV magot (XuanTie C906) és egy második 32 bites RISC-V BL602 ( ESP32-C ) SoC-ra épülő SoC alapú fejlesztési SBC kiadását a vezeték nélküli hálózati rész számára, amelyhez az illesztőprogramok fejlesztés alatt állnak. egy. A cél egy 15 dollárnál alacsonyabb ár (USA), annak érdekében, hogy a fejlesztői platform minél több ember számára elérhető legyen.

Laptop

A Kínai Tudományos Akadémia bejelentette2021. június, hogy 2000 RV64GC alapú laptop kiadását készíti elő 2022 végéig, és ehhez a Firefox motorok ( spiderMonkey és annak on-the-fly fordítója (JIT)) és Chrome / Chromium optimalizálásához szükséges munkát végzi. ( WebKit ), hogy ott megfelelően működjenek.

Szerverek

Az Alibaba csoport a XuanTie 910 (vagy XT910), a szerverek SoC- ját tervezte , amely 16 64 bites RISC-V RV64GCV magból áll, 4 mag 32 vagy 64 kb adat-gyorsítótárral és annyi gyorsítótárral rendelkező fürtökbe rendezve. utasítás. A csoport azt állítja, hogy a mag teljesítménye azonos sorrendben van, mint az ARM Cortex-A73 .

Szuperszámítógépek

Az Európai Unió egy RISC-V architektúrán alapuló szuperszámítógépes projektet indított el , az úgynevezett European Processor Initiative (EPI) nevű projektet , amelyet az EU horizon 2020 program finanszírozott, és amelyet 26 partner (köztük a RISC-V Alapítvány, a Centro Nacional de Supercomputación) fejlesztett ki. (CNS vagy BSC), CEA , Infineon vagy akár STMicroelectronics ) 10 országból. A RISC-V architektúrát a gyorsítókhoz Európában kifejlesztett SoC célja egy exascale szuperszámítógép előállítása, valamint az európai technológiákon alapuló autóipar biztosítása . Az ARM architektúra fő processzorként történő használata tervezett, de nem biztos, ebben az esetben a RISC-V a számítási gyorsítókra korlátozódna. A projekt a meglévő rendszerek újrafelhasználására törekszik (már GNU / Linux alatt megvalósítva ).

Függelékek

Megjegyzések és hivatkozások

- (in) " RISC-V: An Open Standard for SoCs " , EE Times (hozzáférés: 2014. augusztus 17. )

- (en) Lucian Armasu, „A nagy technikás játékosok kezdik alkalmazni a RISC-V chip architektúrát ” , Tom hardverén ,2017. november 29

- (en) Lucian Armasu, "Az Nvidia állásajánlatok rámutatnak az ambiciózus RISC-V tervekre " , Tom Hardware oldalán ,2019. október 10

- (a) William G. Wong, " The Rise of RISC-V látható Workshop " , a ElectronicDesign ,2017. december 5

- (in) Chris Williams, " felfegyverzett! Arm elpusztítja az anti-RISC-V kenet telek után saját munkatársai lázadás ” , a The Register ,2018. július 10

- (in) Joel Hruska, " ARM RISC-V megöli a honlapján után FUD személyzeti Revolt " on ExtremeTech ,2018. július 12

- (in) Nathaniel Mott, "A TSMC nem akarja az USA-ban gyártani a zsetonjait " , a Tom Hardware-en ,1 st november 2019

- (en) Nathaniel Mott, „ Jelentés: A RISC-V tervei az USA-ból Svájcba költöznek ” , Tom hardveréről ,2019. november 26

- "A RISC V Svájcba költözik, hogy elkerülje a kínai-amerikai kereskedelmi háborút " , a 01Net-en

- (en) Jean-Luc Aufranc, „ Hi3861 alapú HiSpark WiFi IoT fejlesztőtábla támogatja a LiteOS-t és a HarmonyOS-t ” , a CNX-Software-en ,2020. október 12

- (in) Gareth Halfacree, " René Rebe folt a Linux Kernel" A világ első "Nézd meg a Radeon 6700XT volt RX RISC-V PC " on hackster.io ,2021. július 21

- (in) " BOOM nyílt forráskódú RISC-V mag fut az Amazon EC2 Instances F1-en " a CNX szoftveren ,2018. december 13

- (en) Jean-Luc Aufranc, „ RISC-V alapok és kiterjesztések magyarázata ” , a CNX-Software-en ,2019. augusztus 27

- Waterman és Asanović 2019 , p. 35.

- Jim Ledin, " The RISC-V Architecture " , a DZone- on ,2020. június 5

- (in) Andrew Waterman és Krste Asanović A RISC-V Instruction Set ManualVolume I: felhasználói szintű ISA Dokumentum verzió 2.2 , CS Division, EECS Department, University of California, Berkeley,2017( online olvasható ) , p. 27.

- (en) fejezete. 5 „RV64I alapösszegű utasításkészlet, 2.1-es verzió” , a RISC-V utasításkészlet kézikönyvében, I. kötet: RISC-V felhasználói szintű ISA, 20191214–2019. December ,2019 december( online olvasás )

- (in) RISC-V "V" vektor kiterjesztés ( olvasható online )

- (in) Jon Peddie, " RV64X: egy ingyenes, nyílt forráskódú GPU RISC-V " az EE Times ,2021. január 27

- (en) Jean-Luc Aufranc, " Think Silicon NEOX | V is the first RISC-V ISA based GPU " on CNX-Software ,2019. december 4

- (in) " Kazan " a salsa.debian.org oldalon

- (in) " Letöltés - RISC-V " a riscv.org címen hozzáférés dátuma = 2014. augusztus 17

- Alicia Daleiden, „ Rust Comes to RISC-V ” a Riscv.org oldalon ,2017. november 28

- Andrew Back, “ Rust Comes to RISC-V ” , az ABopen oldalán ,2017. november 28

- https://bronzebeard.readthedocs.io/en/latest/

- (in) " Minimális ökoszisztéma a csupasz fém RISC-V fejlesztéséhez pythonban " a Python Awesome.com webhelyen ,2021. június 29

- https://github.com/theandrew168/derzforth

- " [base] Revision 295041 " , svnweb.freebsd.org címen (hozzáférés : 2016. január 29. )

- " RISC-V poszter előnézet - 7. RISC-V műhely " ,2017. november 28(megtekintve 2018. december 17. )

- (in) " Gd32v " az Arduinolibraries.info oldalon

- (a) " Zephyr " a RISC-V kezdési útmutatójában (a readthedocs.io oldalon)

- (in) " Minimálisan támogatott verzió rozsda (MSRV) " a Comtpe Rust-on beágyazva a Github-ba

- (in) oscourse-Tsinghua a Githubon, " RCORE "

- (in) "A RISC-V egy nyílt forráskódú utasításkészlet-architektúra, amely utat nyit a számítástechnikai innováció és tervezés elkövetkező 50 évében. » , A tessentembeddedanalytics.com oldalon

- (in) " Ghidra Software Reverse Engineering Framework " a Githubon

- (in) " " ghidra / Ghidra / processzorok Ghidra_9.2_build " " A siource a Ghidra kódot GitHub ,2020. november 13(megtekintés : 2020. november 21. )

- (en) Jean-Luc Aufranc, " Android 10 átírták RISC-V fedélzeti powered by Alibaba T-Head XuanTie C910 Processor " on CNX-Software ,2021. január 22

- (a) " RISC-V " -ben a Debian .org webhelyen

- https://fedoraproject.org/wiki/Architectures/RISC-V

- (en) " Ubuntu 20.04 / 21.04 64 bites RISC-V kiadva QEMU, HiFive táblákra " a CNX szoftveren ,2021. június 28

- https://github.com/riscv/meta-riscv

- https://wiki.freebsd.org/riscv

- https://discuss.haiku-os.org/t/my-haiku-risc-v-port-progress/10663

- https://discuss.haiku-os.org/t/my-progress-on-real-risc-v-hardware/10963/30

- https://www.youtube.com/watch?v=wHp-UIGov8c

- (in) " Getting Started with RISC-V " a riscv.org oldalon (hozzáférés: 2014. augusztus 17. ) , archívum

- (in) " riscv-tools " a riscv.org oldalon (hozzáférés: 2016. július 11. )

- (in) " ChangeLog / 2.12 - RISC-V " a qemuban

- (in) " QEMU System Emulation User's Guide " , qemu (hozzáférés: 2021. január 31. )

- (in) " Haiku RISC-V kikötőm előrehaladása " a Haiku-os.org oldalon

- (in) A3F, " bareDOOM " a BareDoom-on a Githubon

- (in) " JuiceVm " a juiceRv számlán a Githubon

- (in) "A Linux 5.0 bemutatja az ESP32 processzor indítását " a CNX-Software-en ,2021. július 18

- (in) " riscv-rust " a Githubon

- Abhishek Jadhav, „ WARP-V: A MIPS ISA-t támogató RISC-V CPU maggenerátor ” , a CNX-szoftveren

- " A NEORV32 RISC-V processzor "

- (in) " A NEORV32 processzor (RISC-V) " az OpenCores.org oldalon

- " A NEO430 processzor " , a Githubon

- (in) Gareth Halfacree, " kínai chip tervezők remélik, hogy elbukik élesítés Cortex-A76 a Xiangshan RISC-V kialakítás Permissively engedélyezett, a processzor a második iteráció célozza meg 2GHz 14nm " , a The Register ,2021. július 6

- (in) " PicoRV32 - méretre optimalizált RISC-CPU V " a GitHub-on

- "A Codasip megkönnyíti a Western Digital RISC-V SweRV Core nyílt forráskódú hardveres megvalósítását " , www.lembarque.com (Hozzáférés : 2021. május 20. )

- "A Codasip kiterjeszti a Western Digital RISC-V SweRV magok támogatását beágyazott modellekre " , www.lembarque.com (elérhető: 2021. május 20. )

- " OpenXiangShan / XiangShan " , a Github OpenXiangShan fiókján

- (zh)包 云岗, „ 首届 RISC-V 中国 峰会 2021 年 6 月 21 日 起 在 上海 举行 , 有 什么 值得 关注 的 地方? ” , on知 乎

- (en) Jean-Luc Aufranc, „ XiangShan nyílt forráskódú 64 bites RISC-V processzor az Arm Cortex-A76 riválisával ” , a CNX-Software-en ,2021. július 5

- (in) „ Kínai Tudományos Akadémia kiadta a hazai RISC-V processzor” Xiangshan „qui sikeresen Linux fut, és fel kell szabadítani júliusban ” szóló min.news ,2021. július 2

- (in) Nicole Hemsoth, " Startup kockázatot vállal a RISC-V Custom Silicon " , a következő platform ,2016. július 11

- Alasdair Allan: „ Végre felszáll a RISC-V? » , A Hacksters.io webhelyen ,2018. február 19

- (in) " Processzorok " a shakti.org.in oldalon

- (in) "A Codasip csatlakozik a RISC-V Alapítványhoz és bejelenti a RISC-V Codix-kompatibilis processzor IP elérhetőségét " a tervezésnél és újrafelhasználásnál (hozzáférés: 2021. május 20. )

- "A Codasip bemutat 3 többmagos RISC - V processzort az IA Edge számára " , az Electronics-ECI oldalon ,2020. december 8(elérhető : 2021. május 20. )

- "A Codasip lehetőséget kínál a RISC-V processzor valós megvalósításának gyakorlására " , a www.lembarque.com oldalon (elérhető : 2021. május 20. )

- (en) Jean-Luc Aufranc, "A GreenWaves GAP8 egy alacsony fogyasztású RISC-V IoT processzor, amely mesterséges intelligencia alkalmazásokhoz van optimalizálva " a CNX-szoftveren , 2018. december 27-én.

- (en) GigaDevice Semiconductor Inc. GD32VF103 Felhasználói Kézikönyv ,2019. október, 533 p. ( online olvasás )

- Gerhard Steizer, " RISC-V mindenkinek " , az Elektronknet.de oldalon ,2019. szeptember 4

- (en) Jean-Luc Aufranc, " GigaDevice GD32 egy gyorsabb, szoftver és Pin-to-pin kompatibilis Cortex M3 STM32 MCU " on CNX-Software ,2015. december 21

- (in) Brian Benchoff, " New Day rész: A RISC-V Chip beépített Neural Networks " a Hack a Day ,2018. október 8

- Kadionik Patrice, " Maixduino: Csinálj AI-t egy RISC-V processzoron ", feltörhető , n ° 36 hónap = január,2021( online olvasás )

- (in) " Kendryte K510 hárommagos RISC-V AI processzor akár 3 TOPS-t szállít " a CNX szoftveren ,2021. július 9

- (en) Jean-Luc AUFRANC, " NodeMCU ESP32-C3 WiFi & BLE tárgyak internete táblák mutatják fel körülbelül $ 4 " on CNX-Software ,2021. július 12

- (en) Jean-Luc Aufranc, „ OpenWiFi nyílt forráskódú, Linux-kompatibilis WiFi-verem fut az FPGA hardveren ” , a CNX-szoftveren ,2019. december 16

- (en) Jean-Luc Aufranc, " BL602 / BL604 RISC-V WiFi és Bluetooth 5.0 LE SoC fogja eladni áron pontokat ESP8266 " on CNX-Software

- (en) Jean-Luc Aufranc, " ESP32-C3 WiFi & BLE RISC-V processzor pin-to-pin kompatibilis ESP8266 " on CNX-Software ,2020. november 22

- (in) Gareth Halfacree, " mély neurális hálózatok ... IN SPAAACE: Vector megnövelt RISC-V chips adhatna fedélzeti műhold " , a The Register ,1 st július 2021

- Di Mascio és Al 2021 .

- (in) Gareth Halfacree, "A fenyő megrendeléseket nyit meg a RISC-V meghajtású forrasztópáka intelligens készülékéhez - ingyenes kitörési táblával " a Hackster.io oldalon ,2020. november 25

- (en) Jean-Luc Aufranc, " $ 3,5 RV-Debugger Több JTAG hibakereső UART deszkával jön BL702 BLE & ZigBee SoC RISC-V " on CNX-Software ,2021. június 21

- (in) " LicheeTang Anlogic EG4S20 FPGA Board Célozza a RISC-V Fejlesztést " a CNX szoftveren ,2018. szeptember 4

- “ 5 dolláros Tang Nano FPGA alaplap GOWIN GW1N“ LittleBee ”FPGA ” -ot tartalmaz a CNX szoftveren ,2019. október 15

- (hu + zh) „ Hummingbird E200 Opensource Processor Core ” , a GitHubon

- (en) Jean-Luc Aufranc, " Efinix Releases Három RISC-V szoftver által meghatározott SoC optimalizálva FPGA Trion " a CNT-Software ,2020. június 6

- (en) Jean-Luc Aufranc, " PolarBerry egy kompakt Linux képes RISC-V FPGA modul és az SBC (crowdfunding " a CNX Software ,2020. július 5

- (en) Jean-Luc Aufranc, " PUpcoming SAVVY-V nyílt forráskódú RISC-V Cluster tanács támogatja 10GbE keresztül Microsemi PolarFire 64 bites RISC-V SoC " szóló CNX Software ,2020. július 20

- (en) Jean-Luc Aufranc, " PolarBerry egy kompakt Linux képes RISC-V FPGA modul és az SBC (crowdfunding " a CNX Software ,2020. október 30

- (en) Jean-Luc Aufranc, "A SiFive bemutatja a HiFive Unleashed RISC-V Linux Fejlesztő Testületét (Crowdfunding) " a CNX szoftveren ,2018. február 4

- (en) Jean-Luc Aufranc, " PicoRio Linux RISC-V SBC egy nyílt forrású alternatíva a Raspberry Pi board " on CNX-Software ,2020. szeptember 4

- Jean-Luc Aufranc, " XuanTie C906 alapú Allwinner RISC-V processzor 12 dollár + Linux SBC-k áramellátására " , a CNX-szoftveren ,2020. november 9

- Jean-Luc Aufranc, „ 119 USD + BeagleV erőteljes, nyílt hardveres RISC-V Linux SBC célozza az AI alkalmazásokat ” , a CNX-Software-en ,2021. január 13

- (in) Chloe Ma, " RISC-V csillag Rising a kelet - Bemutatjuk StarFive " on riscv.org ,1 st március 2021

- (zh) " 重磅 " , a Starfive számlán a Weixin-en ,2020. december 10

- (in) Starfive Tech, " BeagleV Starlight RISC-V Fedora kép " a Gihtubon

- (in) PINE64, " Februári frissítés: mutasd és mondd " a Pine64.org oldalon

- (in) Gareth Halfacree, " Kína ISCAS építeni 2000 RISC-V laptopok végére 2022 a nemzet igyekszik vágott Reliance Arm, Intel chipek " , a The Register ,2021. június 8.

- (en) Jean-Luc Aufranc, " További részletek az Alibaba XT910 64 bites RISC-V Core rendszerről " a CNX szoftveren ,2020. augusztus 25

- (in) " Hogyan fejleszti az európai kezdeményező processzorok kihasználását a RISC-V a szuperszámítógép jövőjére " a HPC belsejében ,2019. augusztus 22

Irodalomjegyzék online

-

(en) „ Specifikációk ” , a riscv.org oldalon

- (en) Andrew Waterman és Krste Asanović, A RISC-V utasításkészlet kézikönyve - I. kötet: Kiváltságtalan ISA , CS osztály, EECS Tanszék, Kaliforniai Egyetem, Berkeley,2019 december( online olvasás )

- (en) Andrew Waterman és Krste Asanović, A RISC-V utasításkészlet kézikönyve - II. kötet: Kiváltságos építészet , CS osztály, EECS Tanszék, Kaliforniai Egyetem, Berkeley,2019. június( online olvasás )

- (en) Krste Asanović (en) és David Patterson , az utasításkészleteknek szabadnak kell lenniük : A RISC-V esete , Kaliforniai Kaliforniai Villamosmérnöki és Számítástudományi Egyetem, Berkeley,2014. augusztus( online előadás , online olvasás )

- (Elavult) A RISC-V utasításkészlet HotChips 25 (2013)

- A RISC-V szoftver ökoszisztéma HPCA 2015, oktatóanyag

- Yunsup Lee, RISC-V „Rocket Chip” SoC Generátor vésőben , UC Berkeley, HPCA,2015( online olvasás )

- (en) d0iasm, RISC-V emulátor írása Rust-ban ( online olvasható )( forrás )

- en) Hiroaki Kaneko et Akinori Kanasugi, Integrált gépkód- monitor RISC-V processzorhoz FPGA-n , SpringerLink,2020( ISSN 1614-7456 , OCLC 1196515116 )

- en) Johannes Geier, a gyors RTL-alapú hibajuttatási keretrendszer a RISC-V magokhoz , München, Masterarbeit Technische Universität,2020( OCLC 1193312286 )

- (en) SHAKTI fejlesztői csoport, RISC-V közgyűlés Nyelv: Programozói kézikönyv I. rész , Madras, SHAKTI fejlesztői csoport,2020( online olvasás )

- en) Stefano Di Mascio, Alessandra Menicucci, Eberhard Gill, Gianluca Furano és Claudio Monteleone, „ Fedélzeti döntéshozatal az űrben mély neurális hálózatokkal és RISC-V vektoros processzorokkal ” , Journal of Aerospace Information Systems ,2021. június( DOI 10.2514 / 1.I010916 , online bemutató , online olvasás )

Irodalomjegyzék papíron

Művek- en) Andrew Shell Waterman, a RISC-V utasításkészlet-architektúra tervezése , Berkeley, Kalifornia,2016( OCLC 957714390 ) (disszertáció Ph.D.-hez a Kaliforniai Számítástudományi Egyetemen, Berkeley, 2016)

- en) John L. Hennessy és David A. Patterson, Számítógépszervezés és tervezés RISC-V Edition , Morgan Kaufmann,2017. április, 696 p. ( ISBN 978-0-12-812275-4 , e-ISSN 978-0-12-812276-1 [ellenőrzés: Érvénytelen ISSN ] )

- (zh-Hans)胡振波,手把手教 你 设计 CPU : RISC-V 处理器 篇, 北京, 人民 邮电 出版社,2018. május, 480 p. ( ISBN 978-7-115-48052-1 , online előadás )

- (ja)デ イ ビ ッ ド · パ タ ー ソ ン (David A Patterson) és ア ン ド リ ュ ー · ウ ォ ー タ ー マ ン (Andrew Waterman) ( ford .成 田光彰 (Narita)), RISC -V 原 典 (リ ス ク フ ァ イ ブ 原典 典): オ ー プ ン · ア ー キ テ ク チ ャ のス ス メ, 日 経 BP2018, 224 p. ( ISBN 978-4-822292-812 )

- Gaétan Kuetche Saadeu, RISC-V többmagos mikrovezérlő megtervezése Bevezetés az Arduino Shields alkalmazásával készült mikrovezérlő tervezésébe , Saarbrücken, European University Publishing,2019( ISBN 9786139502493 )

- (en) John L Hennessy és David A Patterson, Számítógép-építészet: kvantitatív megközelítés , Cambridge, Massachussetts, Elsevier, koll. "Morgan Kaufmann sorozat a számítógép építészetében és tervezésében",2019( ISBN 9780128119068 )

- (zh-Hans)胡振波, RISC-V 架构 与 嵌入式 开发 快速 入门, 北京, 人民 邮电 出版社,2019, 354 p. ( ISBN 9787115494139 )

- en) Anthony J Dos Reis, RISC-V gyülekezési nyelv , Egyesült Államok,2019, 149 p. ( ISBN 9781088462003 )

- (en) Jim Ledin, Modern számítógépes architektúra és szervezet: Ismerje meg az X86, ARM és RISC-V architektúrákat és okostelefonok, PC-k és felhőszerverek tervezését , Birmingham, Packt Publishing,2020( ISBN 978-1-838987-107 )

- Shruthi K Muchandi, az Accelerator-SoC együttes tervezésének lehetővé tétele a RISC-V Chipyard segítségével , Charlotte, Észak-Karolinai Egyetem,2020( ISBN 9781392495506 )

- en) Jing Chen, Hardveres gyorsítás az alapfunkciókhoz és a RISC-V processzor , Montreal, McGill University Libraries,2020( OCLC 1199006597 )

- (en) Vladimir Herdt, Daniel Große és Rolf Drechsler, továbbfejlesztett virtuális prototípus: RISC-V esettanulmányok , Cham, Springer,2021( ISBN 978-3-030-54827-8 , DOI 10.1007 / 978-3-030-54828-5 )

- Kadionik Patrice, " Maixduino: csinálj AI-t egy RISC-V processzoron ", Hackable , n o 36,2021. január( online olvasás )

Külső linkek

- http://riscv.org/ - Hivatalos webhely

- http://www.eecs.berkeley.edu/Pubs/TechRpts/2014/EECS-2014-146.pdf - RISC-V utasításkészlet és összehasonlítás más hasonló architektúrákkal.

- https://riscv.org/software-tools/riscv-angel/ - ANGEL, RISC-V utasításkészlet HTTP szimulátor

- (en) „ A RISC-V utasításkészlet-architektúra elemzése ” , az Adapteva oldalon - összehasonlítás a RISC-V architektúra (32 bites verzió) és az Adapteva architektúra között.

- (en) " RISC-V " , a wiki.debian.org oldalon, a Debian kikötője a RISC-V-n

- (en) " RISC-V magok és SoC áttekintés " , a Félelmetes nyílt forráskódról - megvalósítások listája